The flip-flops in the synchronous counters are all driven by a single clock input. 1- to Enable the.

How To Design And Experiment A Synchronous Counter Using 74ls73 Jk Flip Flop To Count Decimal 1 2 5 7 Quora

I hooked up a standard counter using T flip flops and AND gates and then for the parallel load I created a load input that runs into 4 2-1 MUXs.

. After it reaches its maximum value of 15 calculated by 24-1 it resets to zero. Parallel load counter can be used to create any desired count pattern. Hint consider how you might use a MUX here.

Design a four-bit synchronous counter with parallel load. Design a four-bit synchronous counter with parallel load. 4_bit_synch_counter_w_loaddoc 1 1 4-bit synchronous binary counter w parallel load Figure 614 of text.

Design Specification. It has two inputs of STD_LOGIC Clock and Reset. Its operating frequency is much higher than the.

515 Design a three-bit updown counter using T flip-flopsIt should include a control input called UpDownIf UpDown 0 then the circuit should behave as an up-counterIf UpDown 1 then the circuit should behave as a down-counter. Download scientific diagram 4-Bit Binary Counter with Parallel Load. Fundamentals of Digital Logic.

Design a four-bit synchronous counter with parallel load using T flip-flops and other gatesbuilding blocks. The Counter will be. To design a synchronous up counter first we need to know what number of flip flops are required.

In the above image the basic Synchronous counter design is shown which is Synchronous up counter. This is accomplished by using the J and K inputs and is illustrated in. The counter is a digital sequential circuit and here it is a 4 bit counter which simply means it can count from 0 to 15 and vice versa based upon the direction of counting updown.

At first we have twoo main states. Synchronous means to be driven by the same clock. You can see the logic circuit of the 4-bit synchronous up-counter above.

Each digit in a number is represented by one of A counter with parallel load can be used to 10 characters 0-9. Design of Counters with Parallel Load Asynchronous Load Synchronous Load Modular Counters. Synchronous Counter design procedure for a given counting sequence.

Design a four-bit synchronous counter with parallel load. Each probe measures one bit of the output with PR1 measuring. 2- we can enable the load regardless of the value of the count.

So in this we required to make 4 bit counter so the number of flip flops required is 4 2 n where n is a number of bits. Overview of this design. Using the load input.

Synchronous Parallel-Carry Binary Counter. Design steps of 4-bit synchronous counter count-up using J-K flip-flop. Synchronous Parallel Counters Synchronous parallel counters.

Use T flip-flops instead of the D flip-flops used in Section 593. The circuit shown below a reset pulse has been applied and outputs Q0 through Q5 have all been reset to 0 a-5 points Create a truth table for. These gates build a counter circuit.

Please Like Share and subscribe to my channel. See figure attached for my attempt. We can find out by considering a number of bits mentioned in the question.

With VHDL Design with CD-ROM 2nd Edition Edit edition Solutions for Chapter 7 Problem 15P. Heres a great problem to put into Logisim. 2-bit synchronous binary counter using T flip-flops or JK flip-flops with identical JK inputs.

Using the clear input. A 4-bitcounter with parallel load can be helpful to produce a BCD count in two major ways which are given below. We can design these counters using the sequential logic design process covered in Lecture 12.

Design a four-bit synchronous counter with parallel load using T flip-flops. This 4-bit digital counter is a sequential circuit that uses JK flipflops AND gates and a digital clock. Design a four-bit synchronous counter with parallel load.

If load 0 then it will spit out the output of the preceding flip flop. 4-bit synchronous up counter. For parallel load functionality View the full answer Transcribed image text.

It is a digital circuit that performs counting in binary numbers with the help of flip-flops and all flip-flops triggered simultaneously. As the input clock pulses are applied to all the Flip-flops in a synchronous counter some means must be used to control when an FF is to toggle and when it is to remain unaffected by a clock pulse. Identify the numbers of flip-flops FFs inputs and outputs required for.

Text problem 514 Design a four-bit synchronous counter with parallel load using T flip-flops. 514 Design a four-bit synchronous counter with parallel loadUse T flip-flops instead of the D flip-flops used in Section 593. Design of a nanometric reversible 4-bit binary counter with parallel load In recent years reversible.

Counters employed in digital systems quite often require a parallelload capability for transferring an initial binary number into the counter prior to the c. Because this is a synchronous counter then we will assume that Clk is at logic high 1 all the time. Use T flip-flops instead of the D flip-flops used in Section 593.

A 4-bit can only be two characters 0 and 1A counter with parallel load. Use T flip-flops instead of the D flip-flops used in section 793. After that we need to construct.

Synchronous Up Counter. So lets assume that we wanna load the data which is 0010. Design a fourbit binary synchronous counter with D flipflops Complete design steps-----.

The flip-flops are clocked at the same time by a common clock pulse. For each clock tick the 4-bit output increments by one. In a binary system there create any desired count sequence.

Fundamentals of Digital Logic with Verilog Design 2nd Edition Edit edition Solutions for Chapter 7 Problem 15P. A 4-bit Synchronous up counter start to count from 0 0000 in binary and increment or count upwards to 15 1111 in binary and then start new counting cycle by getting reset. The counter count value will be evaluated at every positive rising edge of the clock clk cycle.

And four outputs since its a 4-bit counter. Overview of this design. The load must be at logic 0.

Use T flip-flops instead of the D flip-flops used in section 793.

Synchronous Counters Notes Study Digital Electronics Electrical Engineering Ee

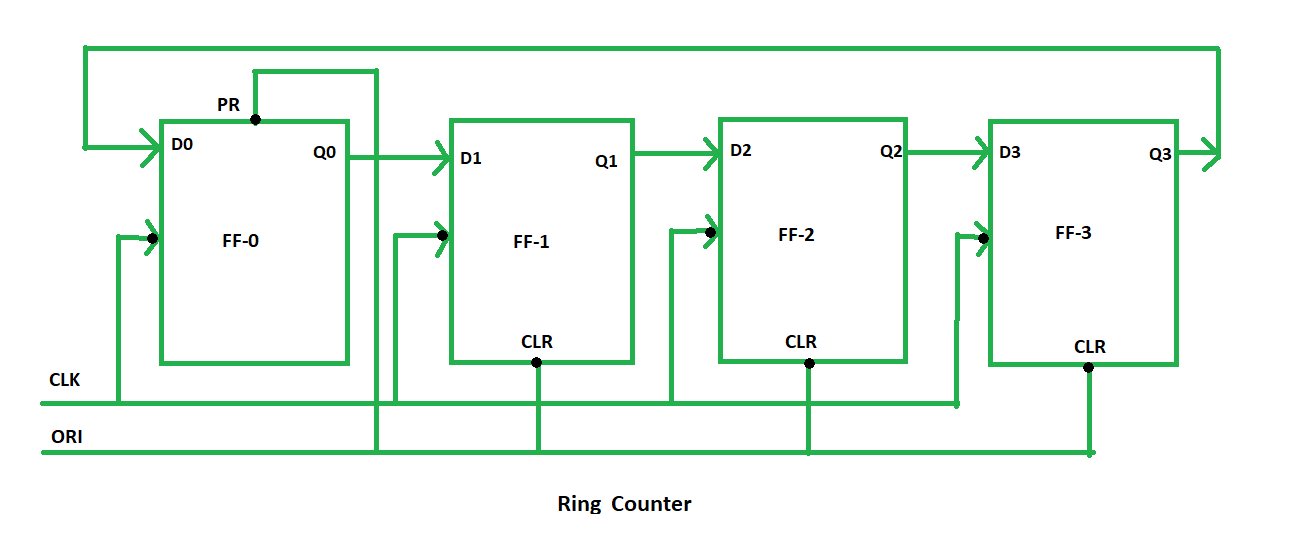

Ring Counter In Digital Logic Geeksforgeeks

Egr 2131 Unit 9 Registers And Counters Ppt Download

Synchronous Counters Notes Study Digital Electronics Electrical Engineering Ee

Synchronous Counters Notes Study Digital Electronics Electrical Engineering Ee

4 Bit Decade Counter Description Glossary Of Electronic And Engineering Terms Ic Up Down Counter

0 comments

Post a Comment